## Das Basic Input/Output System (BIOS)

Hierbei handelt es sich um den hardwareabhängigen Teil des CP/M Betriebssystems. Er nimmt für jedes Computersystem die Anpassung an die spezifische Systemkonfiguration vor. Bedingung an das BIOS ist, daß es mit einer Sprungtafel beginnt, die 17 Routinen (*Tabelle 2*) bedient (ob sich nun wirklich die entsprechenden Routinen dort befinden ist egal, zum Beispiel wird in mc 1980, Heft 3, die Verwendung der READER-Routine für einen Barcodeleser beschrieben).

## CP/M-Hilfsmittel

Mit dem CP/M-System werden eine Anzahl von Hilfsmitteln bereitgestellt, die nach Bedarf von der Diskette geladen werden können. Diese können von Computersystem zu Computersystem variieren, standardmäßig sind sie jedoch vorhanden (Tabelle 3):

## Die Speicherorganisation

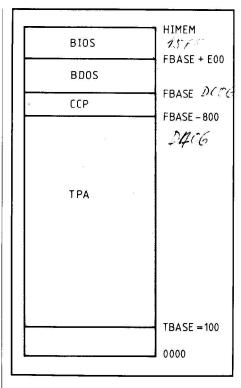

Bild 1 gibt einen Einblick in die Speicherbelegung durch CP/M. Die drei Module sind von der höchsten RAM-Adresse abwärts lokalisiert. Die wichtigsten Adressen sind FBASE, der Beginn des BDOS und die TBASE, der Beginn der "Transient Program Area", des für Anwenderprogramme zur Verfügung stehenden RAMs. Die ersten 256 Byte, die Zero-Page, sind für den Gebrauch durch CP/M freigehalten. Es befinden sich hier (alle Adressen hex):

0-2 Jump WARMBOOT

- Das IOBYTE (Erklärung später)

Das momentan angesprochene

Laufwerk (ab Null zählend)

- 5–7 Jump BDOS (dies ist der Einsprungspunkt für alle BDOS-Operationen, Byte 6 und 7 geben die FBASE wieder, FBASE-1 gibt die größte für Anwenderprogramme nutzbare RAM-Adresse an)

- 8 RST 1 Ansprungpunkt

- 10 RST 2

- 18 RST 3

- 20 RST 4

- 28 RST 5

- 30 RST 6

- 38 RST 7 wird vom DDT-Programm benutzt. Alle anderen Restartadressen sind momentan nicht benutzt.

- 5C- Vom CCP zur Speicherung des7C FCB (File Control Block)

- 80- Vom CCP als File In-/Output-FF Buffer benutzt (DMA-Buffer).

Der genaue Wert der FBASE ist von der jeweiligen Größe des BIOS und des zur Verfügung stehenden User-RAMs abhängig. Bei dem von Digital Research vertriebenen CP/M für das Intel MDS-Intellec-System ist ein Bereich von 1536 Byte freigehalten, die FBASE liegt hier also bezogen auf 64 KByte User RAM bei EC00. Das Heath/Zenith 2.2.02 CP/M hat ein BIOS von 5 KByte, hier liegt – wieder bezogen auf 64 KByte – die FBASE bei DC06. Stets gleich ist die Länge des CCP (800H) und des BDOS (E00H).

## Die Diskettenorganisation

CP/M ist für eine Vielzahl von Diskettenformaten, Aufzeichnungsformen und Kontrollern erhältlich bzw. anpaßbar. Zur Darstellung der Diskettenorganisation soll als Beispiel eine 8-Zoll-Diskette, einfache Schreibdichte, softsektorisiert, dienen. Die 77 Spuren einer solchen Diskette sind in 26 Sektoren mit je 128 Byte Datenspeicherkapazität gegliedert. Dies entspricht dem IBM 3740 Diskettenstandard und solche Disketten heißen deshalb "IBM-kompatibel". Das Speichervermögen einer solchen Diskette beträgt also 77·26·128=256 256 Byte. Jede CP/M-Diskette besitzt drei verschiedene Bereiche. Spur 0 und Spur 1 sind für das CP/M-System reserviert, unabhängig davon, ob es sich überhaupt auf der Diskette befindet.

Spur 0 Sektor 1 Cold Start Loader Spur 0 Sektor 2 bis

Spur 0 Sektor 17 CCP

Spui Osektoi 17 CC

Spur 0 Sektor 18 bis

Spur 1 Sektor 19 BDOS Rest BIOS

Den zweiten Bereich bildet die File Directory Area. Sechzehn Sektoren der zweiten Spur sind stets für das Directory reserviert. Dieser Bereich kann jedoch durch entsprechende Änderungen im BIOS erweitert werden. Der Rest der Diskette wird zur Speicherung von Daten und Programmen benutzt.

Datentransfer von und zur Diskette geschieht in Blöcken zu je 128 Byte. Logisch aufeinander folgende Fileblöcke werden jedoch nicht in entsprechender physikalischer Reihenfolge auf der Diskette abgelegt, da der Disk-Controller nach einem jeden Block erst die Richtigkeit der Übertragung prüfen muß und auch das BDOS einige Zeit bis zur nächsten Lese/Schreiboperation benötigt. Der Standardversatz beträgt sechs Sektoren (ebenfalls IBM-kompatibel), kann jedoch auch anders definiert werden. Die Zuordnung der logischen zur physikalischen Position geschieht über die schon erwähnte BIOS-Funktion 17.

Bild 1. So liegt CP/M im Speicher

Die Verwaltung des Speicherplatzes auf der Diskette erfolgt unter CP/M dynamisch, das heißt, daß zum Zeitpunkt der Neueröffnung eines Files dessen mögliche Länge noch nicht angegeben werden muß. Speicherplatz wird einem File in Portionen zu je 1 KByte zugeordnet. Die Mittel, die CP/M für diese Diskettenverwaltung benötigt, sind:

- 1. Der File Control Block (FCB)

- 2. Die Allocation Bit Map (ABM)

- 3. Das Directory

Ein File Control Block benötigt 36 Byte RAM. Bild 2 zeigt ihn schematisch. Seine einzelnen Teile haben folgende Bedeutung (Tabelle 4):

Die bereits erwähnten 16 Sektoren der zweiten Spur einer jeden CP/M-Diskette enthalten das vom BDOS verwaltete File Directory. Es enthält die jeweils ersten 32 Byte der zu den auf der Diskette befindlichen Files gehörenden File Control Blocks. Bei jedem Neuaufruf einer Diskette liest das BDOS diese 16 Sektoren und berechnet aus den Einträgen in dem DM.-Bereich die Belegung der Diskette. Diese Belegung faßt das BDOS zu der Allocation Bit Map zusammen und legt diese im RAM ab. Diese "Karte" besteht aus 243 Bit und spiegelt die Belegung der Diskette wieder.

Der Ablauf einer Fileeröffnung durch das BDOS auf der Diskette läßt sich nun vollständig beschreiben.

Das BDOS durchsucht die Allocation Bit Map, bis es eine 0 findet.

benutzt.